光刻技术,走下“神坛”

文 | 半导体产业纵横,作者 | 丰宁

您是否曾认为光刻机是芯片制造的唯一关键?但如今,行业巨头们正在重新思考。英特尔一位高管的断言——“光刻将不再那么重要”,瞬间点燃了半导体圈的激烈辩论。

光刻机,长期被奉为半导体制造的命脉。近期多家芯片巨头释放的信号显示,光刻技术正从“唯一解”转向“可选项”,就连炙手可热的High-NA EUV也频频遭遇“冷板凳”。

High-NA EUV光刻机,遭遇市场寒流

去年,High-NA EUV还风光无限。

ASML官网披露,其已组装两台TWINSCAN EXE:5000高数值孔径光刻系统。一台由ASML与imec联合开发,计划2024年入驻联合实验室,2025年量产;另一台由英特尔2018年订购,2023年12月正式交付首批模块。

2024年初,核心组件运抵英特尔;同年11月,台积电宣布年底接收最先进机型;2025年3月,三星在华城园区引入首台设备,成为继英特尔、台积电后第三家用户,并计划用于未来DRAM生产,对手SK海力士也虎视眈眈。

然而现实却是,芯片巨头们纷纷踩下刹车。

英特尔原被视作High-NA EUV的急先锋。

近期数据显示,其工厂已投产两台尖端光刻机,可靠性远超旧款。高级首席工程师Steve Carson透露,凭借High-NA EUV,英特尔单季度可产出3万片晶圆,每片孵化数千计算芯片。

英特尔计划用其助推Intel 18A(1.8nm)技术,预计今年量产;下一代Intel 14A(1.4nm)也将全面依赖该设备,但量产时间仍未公布。

台积电:High-NA EUV大规模应用,至少再等5年

面对High-NA EUV,台积电始终保持冷静。

业务开发资深副总张晓强直言,设备单价超3.5亿欧元令人咋舌。现有EUV光刻机足以支撑尖端制程至2026年,A16工艺将继续沿用标准机型。

在阿姆斯特丹技术论坛上,他再次强调:A16(1.6nm)与A14(1.4nm)工艺均不采用High-NA EUV。

技术团队已攻克A14节点无需High-NA的难题——该设备分辨率达8nm,远超标准EUV的13.5nm。台积电曾考虑将其用于A10制程,但大规模量产恐需等到2030年后。

三星推迟High-NA EUV部署,代工业务从1.4nm起步

即便引进设备,三星也选择观望。

三星与SK海力士双双推迟DRAM产线导入计划,主因是成本高企及DRAM架构变革。按规划,DRAM将从6F²迈向4F²,最终进化至3D DRAM。2030年前量产的4F²需EUV技术支持,但3D DRAM通过堆叠提升密度,或彻底摆脱EUV依赖。

这意味着High-NA EUV在DRAM领域的窗口期可能极短。逻辑芯片方面,三星正评估1.4nm工艺的应用,目标2027年量产。

刻蚀技术崛起,制造策略多维进化

在半导体制造中,刻蚀是与光刻比肩的核心工艺,直接主宰芯片性能与集成度。随着制程杀入3nm以下,刻蚀步骤占比从10%飙升至50%以上——以5nm FinFET为例,刻蚀次数突破150次。

据Tegus平台爆料,一位英特尔匿名总监指出:未来晶体管设计将弱化光刻依赖,转而聚焦刻蚀技术。

GAAFET、CFET等三维结构兴起,正推动芯片制造从“平面雕刻”转向“立体构建”。光刻环节中,ASML设备将电路转印至晶圆;后续沉积添加材料,刻蚀则精准剔除多余部分,塑造晶体管骨架。

该高管强调,三维结构需“包裹式栅极”,横向材料去除成为关键:“制造商更倾向通过刻蚀工艺精修结构,而非一味追求光刻精度。”

简言之,当芯片制造向横向拓展,High-NA EUV的光环自然减弱。与此同时,Lam等刻蚀企业迎来高光时刻。

但光刻机真会退场?绝非如此。

未来制造虽降低对ASML High-NA EUV的依赖,需求仍持续旺盛。该高管解释:“7nm节点时,EUV曾不可或缺,但此后需求渐缓。我们不仅探索横向材料操控,还发力晶圆堆叠技术——逻辑与存储芯片不再挤占单晶圆空间,转而向垂直维度要密度。”

这如同从“铺开郊区”升级为“建造摩天楼”。光刻需求仍在,但角色已变:我们正从单向压缩,迈向双向拓展的制造新时代。

ASML EUV,技术霸权能撑多久?

争议声起,ASML再度被推上风口浪尖。

业界三问:年度出货几何?下一代技术何在?EUV生命周期多长?

2024年财报显示,ASML售出418台光刻机,含44台EUV、374台DUV,另售165套检测系统。

收入版图中,中国大陆贡献101.95亿欧元,占比36.1%稳居榜首;韩国(22.7%)、美国(16.0%)、中国台湾(15.4%)紧随其后。尽管EUV需求推迟,但DUV供不应求,中国市场需求尤其火爆。

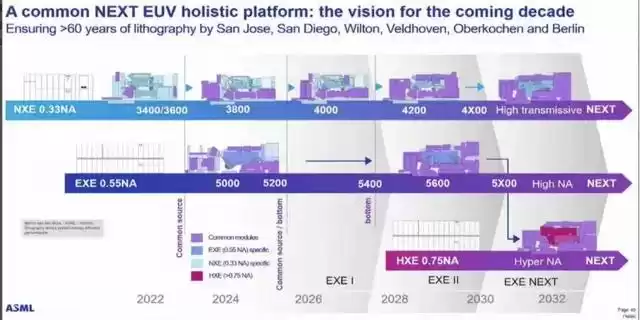

技术迭代方面,ASML与蔡司已瞄准0.75 NA的Hyper NA EUV系统。Jos Benschop称,物镜可贴近芯片以提升效能,虽会增加光反射,但更大数值孔径能加速曝光——如同宽口瓶更易清空。

据路线图,现有EUV可支撑至2025年2nm量产,但1.4nm(2027年)将是其极限。

生命周期层面,ASML垄断全球75%-80%的EUV市场,技术壁垒高筑。EUV重塑芯片产业,未来10-20年仍将举足轻重,但挑战已悄然而至。

新势力崛起,光刻技术群雄并起

当前ASML采用激光等离子体EUV光源(EUV-LPP),但制程推进正逼近其物理极限。美、中、日等国加速研发自由电子激光光源(EUV-FEL),该技术通过粒子加速器产生多波长光,单光源可支持10-20台光刻机,成本大幅降低。

ASML曾评估EUV-FEL,因设备庞大(覆盖整栋建筑)且维护风险高(单点故障波及全线)而弃用。但初创公司Xlight宣布,计划2028年实现EUV-FEL原型与ASML设备对接。

挪威Lace Lithography则另辟蹊径,开发原子光刻技术,用原子取代光子定义特征,分辨率突破EUV极限。其宣称的BEUV可支持晶体管持续微缩,“以原子代光,性能领先15年,成本能耗双降”。

纳米压印光刻、电子束光刻等路线并行发展——前者通过模具压印实现高分辩图形转移,后者凭借电子束直写适用高精度小批量芯片。尽管ASML凭产业链优势暂居主导,但技术多元革命已不可逆。

这场制造范式转移将如何重塑行业格局?您更看好哪种技术路径?欢迎在评论区分享您的真知灼见!

相关问答

什么叫做光刻技术?

光刻技术是集成电路制造的核心工艺,利用光学反应与化学刻蚀,将电路图形精准转印至晶圆表面,形成微纳级功能结构。

世界上最厉害的光刻技术?

目前顶尖光刻技术由荷兰ASML主导,其EUV光刻机以13.5nm极紫外光实现纳米级雕刻,台积电、三星等巨头均依赖该技术突破制程极限。

中科院光刻技术又获新突破,国产芯片距离先进水平还差多远?

国产光刻技术持续攻坚,但在光刻机、光刻胶等关键环节仍存差距,需加速核心技术自主化以摆脱进口依赖。

euv光刻技术深度解析?

EUV光刻以极短波长光源实现超高精度图形转移,通过复杂光学系统与真空环境控制,推动芯片制程跨入纳米时代。

光刻技术主要用于制造芯片,是人类掌握的少数几种?

光刻技术是人类唯一实现大规模芯片制造的工艺,融合光学、化学、物理等多学科精华,支撑现代电子信息产业基石。

目前世界光刻技术达到了什么水平?

全球光刻技术已突破亚10纳米分辨率,支持多层多道光刻流程,助力芯片集成度与性能持续飞跃。

EUV光刻机争夺战打响,国产光刻技术难题有何解?

面对EUV设备垄断,国产技术需在光源、镜头、材料等环节突破,通过产学研协同创新构建自主产业链。

国产光刻技术进展如何?

国产光刻技术近年进展显著,多家企业实现设备与材料突破,正逐步缩小与国际领先水平的差距。

紫外光刻技术?

紫外光刻以特定波段光源通过光学系统投射图形,其分辨率与波长、数值孔径等参数直接相关,是微电子制造基础技术。

新光刻技术被验证,有打破西方技术封锁的希望吗?

新兴技术路线不断涌现,通过原始创新与差异化突破,有望在部分领域实现弯道超车,重塑全球技术竞争格局。