案例:高性能数字、混合信号和射频RF无线产品的EMI/EMC及共存仿真

您是否曾为产品EMC测试失败而苦恼?现代高性能电子系统的设计复杂度正呈指数级增长,集成高速数字接口(如HDMI 2.0、USB 3.1、LP/DDR4)已成为标准配置,但这使得满足严苛的EMI/EMC标准变得空前困难。更棘手的是,系统内WiFi、蓝牙等射频无线接口与高速数字链路间的共存问题,会引发电磁干扰,直接导致射频灵敏度下降、带宽紧缩。问题若在后期爆发,往往意味着代价高昂的重新设计和量产延迟。

本文将基于我们在消费电子、汽车电子等领域的实战经验,为您揭示一套创新的仿真方法,用于精准评估、定位和解决辐射EMI/EMC及耦合问题。

我们将首先剖析典型的射频干扰案例与EMC标准,进而通过详实的仿真分析,展示Ansys EMI/瞬态联合仿真流程的威力。与实测数据的高度相关性验证,是评估各类电磁干扰抑制技术有效性的基石。

直面现实:实现EMC合规与系统共存的设计挑战1、电磁共存(EM Co-Existence)耦合简介

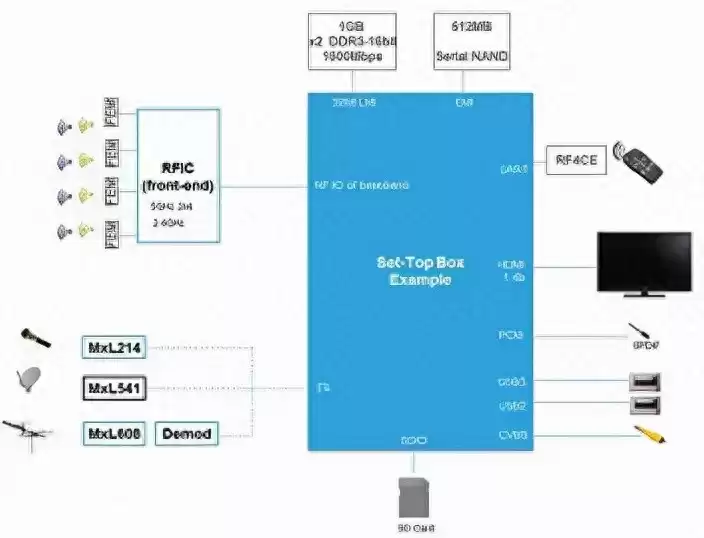

当今的电子系统堪称“功能竞技场”(见图1),高速数字链路(DDR, USB3.1等)与敏感的模拟/RF功能(如WiFi、蓝牙)共存一室。确保它们和平共处是一大挑战。高速数字接口通常是潜在的“干扰源”,当其与RF无线系统同时工作时,必须保证后者仍能维持独立工作时的性能水准。

图1:集成WiFi、HDMI, DDR3等高速接口的典型机顶盒系统

以HDMI 2.0和(LP)DDR3/4为例,它们作为高密度、高速接口,极易引发耦合问题。其通道的差模与共模激励(尤其是差分时钟)会产生强烈的电磁辐射。

另一方面,接收机系统却需要处理极其微弱的信号。例如,WiFi接收机在20MHz带宽下,需能处理低至-82dBm的信号以满足IEEE标准。当WiFi天线紧邻任何潜在的EMI源时,其灵敏度将受到严重威胁,导致射频吞吐量骤降。由于噪声传播路径错综复杂(见图2),定位耦合问题通常既困难又耗时。

图2:电磁噪声在复杂系统中的传播与耦合路径

2、EMI / EMC标准不容忽视

消费类电子产品必须符合各地法规。在欧洲,需满足CISPR22 “Class B”限值。在北美和亚洲,则需符合FCC等标准(示例见图3)。除了电磁发射测试,电磁兼容性测试还包括抗扰度测试,如ESD放电。

图3:芯片(SoC)在1GHz以上的FCC辐射发射测试示例

要避免后期“救火”,就必须从设计之初系统性地规划EMC与共存问题,全面考虑架构选择、技术方案、产品规模及布局布线的优化策略。

利器出鞘:EMI瞬态联合仿真方法详解1、深入理解电磁干扰机理

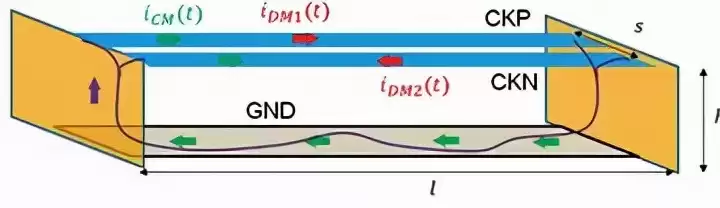

在动用仿真工具前,必须吃透干扰机理。对于数字差分对,存在多种产生EMI的电流激励与环路(图4):差模(DM)激励与环路、共模(CM)激励与环路,以及串扰电流环路。

图4:PCB上差分对的环路几何结构与电流模式

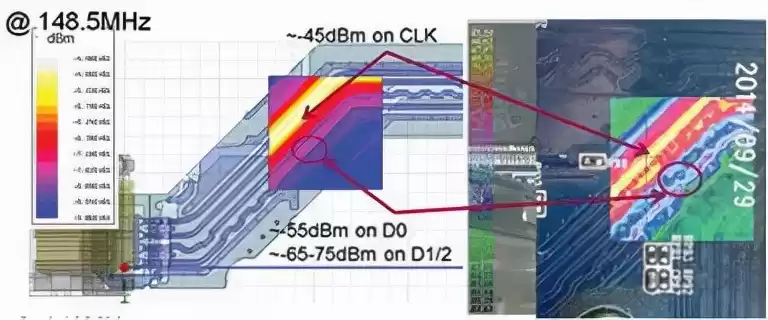

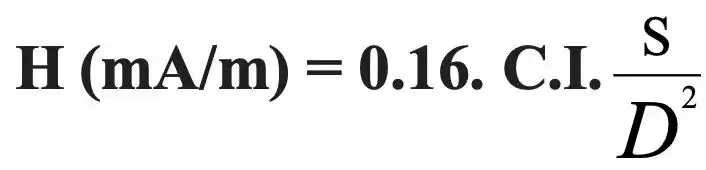

利用理论公式可初步估算辐射场。例如,在近场条件下,数字接口在148.5MHz时磁场占主导,可使用长差分线模型估算。尽管公式因结构复杂性而受限,但仍能获得良好近似(图5)。

图5:磁场理论估算值与仿真值高度吻合

科学近似帮助我们抓住关键:

- 磁近场衰减与1/D²成正比。

- 差模辐射与受标准限值的差模电流成正比。

- 共模辐射由驱动器的平衡性及互连对称性决定。

- 辐射强度与回路面积(由PCB/连接器设计决定)成正比。

2、高保真关联仿真流程

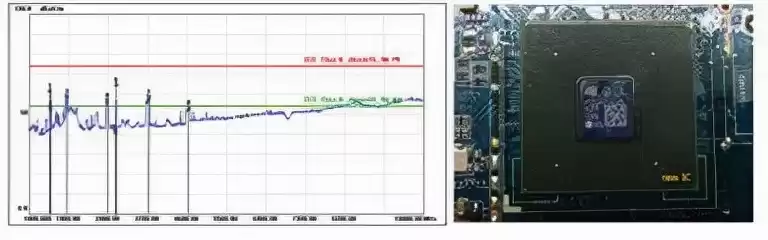

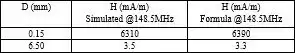

该方法已在高速数字接口案例中通过仿真与测量的成功对比得到验证(图6)。

图6:四对差分线(3数据+1时钟)接口的近场磁场分布

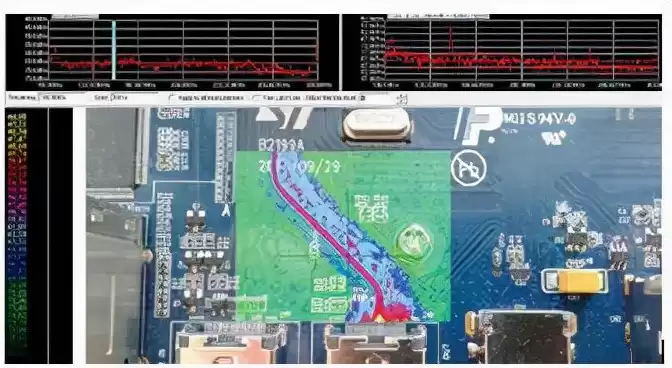

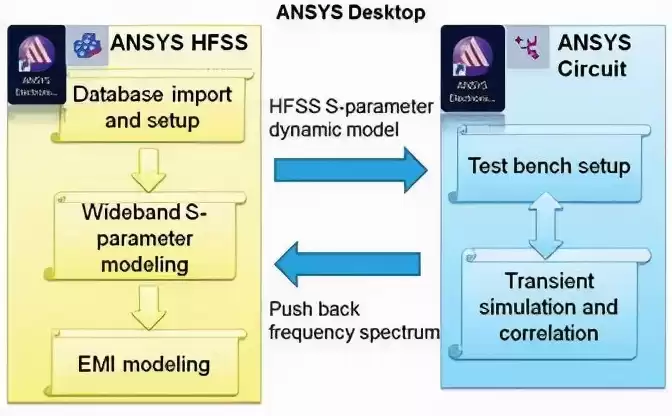

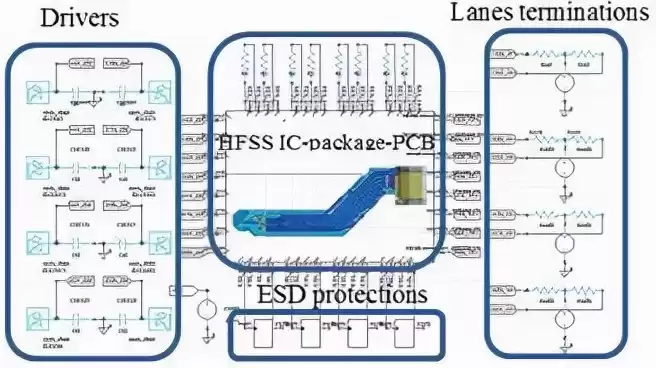

我们采用的Ansys EMI仿真流程核心包括:

- HFSS:用于三维结构建模与全波电磁场计算。

- Ansys Circuit:进行瞬态电路仿真,注入真实激励。

- 数据回馈:将电路仿真结果反馈至HFSS计算最终辐射场。

图7:STMicroelectronics采用的Ansys EMI仿真流程

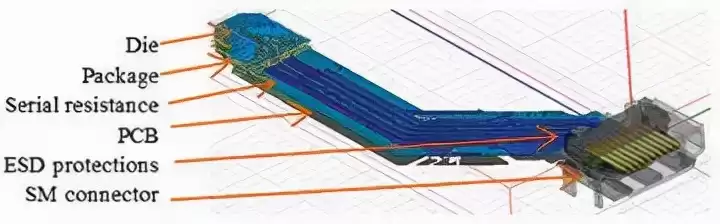

该流程实现了S参数模型与频谱数据的自动交换(图7)。其精髓在于找到精度与仿真速度的最佳平衡点。例如,在HFSS中简化模型至关重要(图8),需要合理设置边界条件、端口、扫频、网格及收敛准则。

图8:HFSS中的3D结构仿真模型

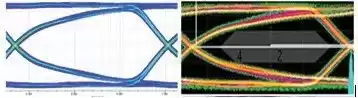

将HFSS的S参数模型导入电路环境并实例化(图9),使用IBIS模型驱动和PRBS码型模拟真实场景。时域仿真后,通过眼图对比验证设置可信度(图10)。

图9:电路环境中集成的HFSS模型原理图

图10:时域仿真(左)与实测(右)眼图高度一致

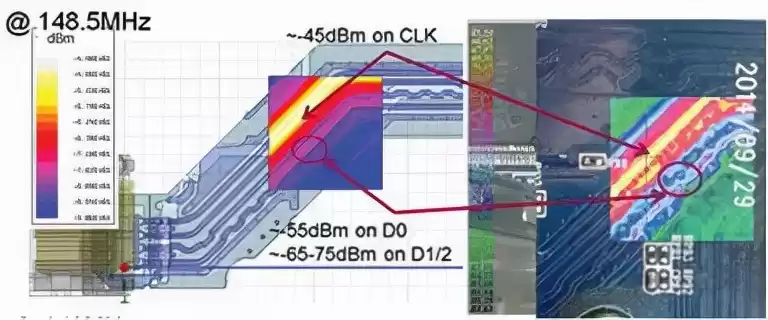

将激励频谱回馈至HFSS重新计算辐射场。为匹配测试条件,需精心设置FFT参数(BW, RBW, 窗函数等)。我们重点关注近场磁场(主导干扰),并在干扰源上方设置扫描面进行评估(图11)。

图11:D=0.15mm处近场磁场的仿真(左)与测量(右)结果对比

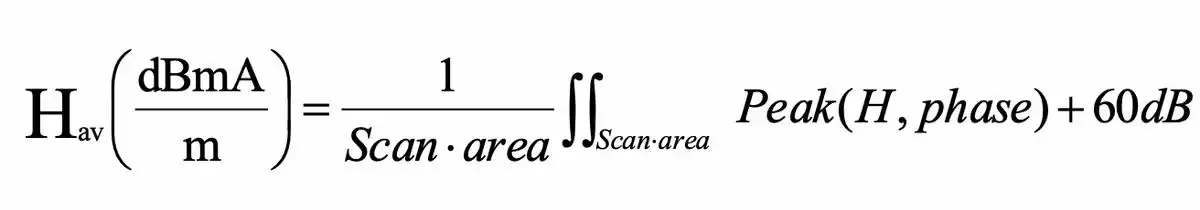

3、量化评估与后处理

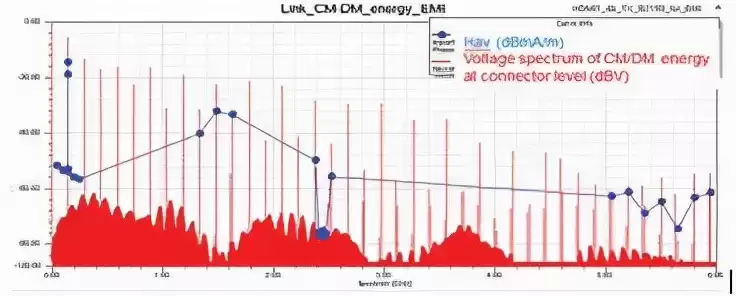

仿真与测量成功对比验证了方法的可靠性。我们定义平均磁场作为评估RF接口干扰风险的关键指标。通过HFSS计算器得到该值在全相位扫描下的最大值。其频域扫描图(图12)是进一步研究优化技术的基准。

图12:TP1点处(d=0.15mm)时钟CM/DM频谱累积效应(红色曲线)

案例分析表明,82%的磁场来自PCB布线,15%来自连接器,仅3%来自封装。但连接器因悬空较高,对EMI的实际影响可能更大,具体取决于RF天线的位置。

实战策略:多管齐下的EMI抑制技术1、功能级抑制技术

若在项目早期实施,功能级技术性价比极高。

- 转换速率控制:熟知的技术。将时钟的转换速率控制在5%-8% UI内,平均可降低频谱约3dB。但需注意其对信号抖动的影响。

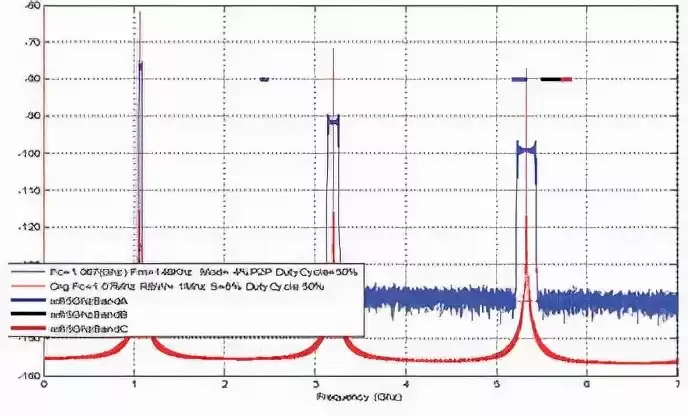

- 扩频时钟:通过频率调制降低峰值能量。在三次谐波处最多可降10dB,五次谐波处达15dB(图13)。

图13:扩频时钟(SSC)技术效果示例

- 数据加扰:通过避免重复位序列来平滑频谱,抑制效果可达20dB。

2、物理级与layout抑制技术

共模噪声常是EMI主因。共模滤波器能有效滤除同相信号。

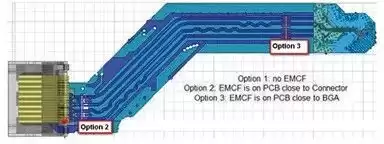

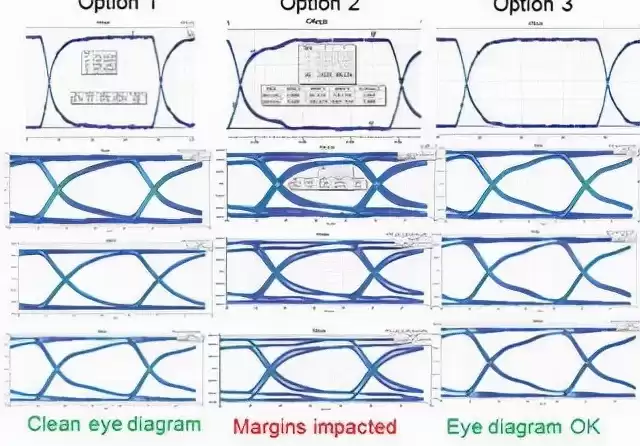

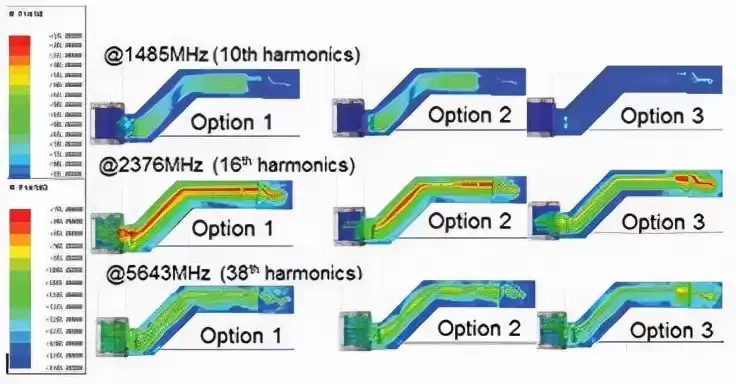

- 共模滤波器布局:位置是关键。将其靠近SoC放置(选项3, 图14),能在1-6GHz内将共模噪声降低15dB,同时保障信号完整性(图15, 16)。

图14:ECMF的三个可能布局位置

图15:不同ECMF布局下的信号完整性仿真对比

图16:ECMF优化布局后的近场磁场仿真(辐射显著降低)

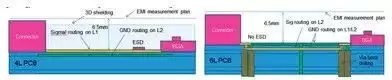

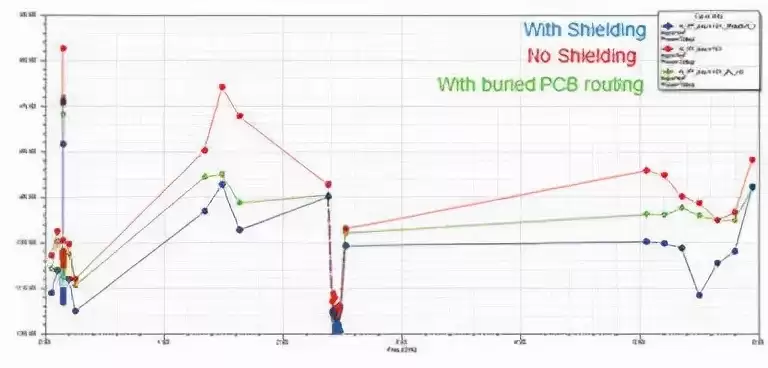

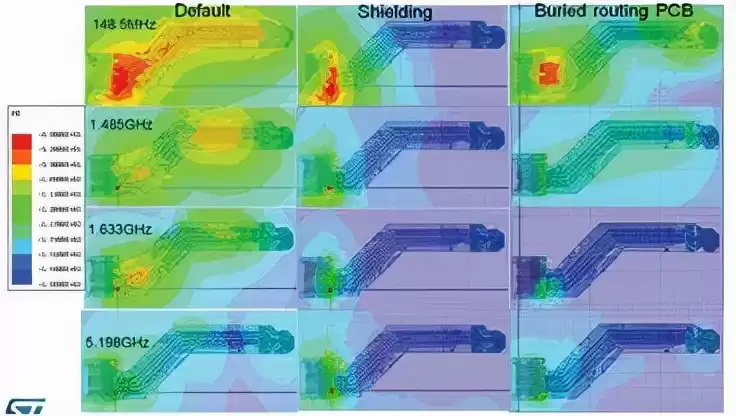

- PCB埋藏走线与屏蔽:经典方法(图17)。对于低成本应用中的敏感过孔,背钻处理是性价比之选。采用埋藏走线时,须警惕谐振问题。屏蔽层若设计不当(如产生腔体谐振),反而会加剧EMI。仿真显示,设计良好的屏蔽(图18, 19)在大部分频段可带来15-20dB的磁场抑制。

图17:表层走线加屏蔽 vs. 埋藏走线的横截面对比

图18:默认DUT、加屏蔽、埋藏走线三者的平均磁场对比(D=6.5mm)

图19:D=6.5mm处的磁场分布图(dBm)

制胜关键:系统化仿真与综合优化Ansys提出的EMI/瞬态联合仿真流程,为应对先进的EMI挑战提供了强大工具。其与实测数据及理论公式的良好相关性,证明了该方法的可靠性与实用价值。

我们的实战经验表明:设计良好的屏蔽层能以低成本提供卓越抑制;共模滤波器能精准打击偶数次时钟谐波;调整RF与数字干扰源的相对位置与方向也是有效手段(近场辐射强度约按1/D²衰减)。同时,功能级调整技术潜力巨大。

行动号召: 面对日益复杂的电磁环境,依赖后期测试整改的传统模式已风险重重。将高保真的EMI/EMC与共存仿真前置到设计周期,是确保产品一次成功、快速上市的必然选择。立即探索系统化仿真解决方案,为您的产品打造坚不可摧的电磁兼容性!

相关问答

展频技术主要有哪些分类?

展频技术核心分为两大流派:跳频技术与直接序列扩频。该技术通过扩展信号频谱来降低单位频点能量,从而有效抑制电磁干扰峰值,是无线通信及高速数字电路应对EMI的常用手段。

展频电路在设计中具体起什么作用?

展频电路的核心作用是主动降低电磁干扰。当时钟发生器工作时,其尖锐的脉冲会产生显著的EMI。展频技术通过调制时钟频率,将能量分散到更宽的频带上,从而显著降低峰值辐射强度,帮助产品更易通过EMC认证。